Inverting Amplifier 반전 증폭기 | (2020-09-19) |

Virtual Ground, 가상 접지 | |

▷

Top

▷

전기전자공학

▷

전자회로

▷

증폭기

▷

연산증폭기

▷

연산증폭기 기초응용

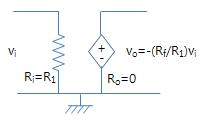

1. 반전 증폭기 (Inverting Amplifier) ㅇ 상수 이득을 갖고, 입력이 반전(180˚ 위상천이) 됨 - 유사 유형 例) 공통 이미터 증폭기, 공통 소스 증폭기, CMOS 인버터 등 ㅇ 연산증폭기 기본 구성 중 하나 (☞ 비반전증폭기 참조) - 연산증폭기는, 개방루프이득이 매우 커서, - 부귀환 없이는 불안정해지므로, - 부귀환을 통해 전압이득을 안정화시키는 연산증폭기 기본 회로의 구성 2. [Op Amp] 반전 증폭기의 회로 구성, 특징 ㅇ 반전 구조 - 비반전 단자(+)를 직접 접지하고, 반전 단자(-)에 입력 전압을 인가하는 구조ㅇ 출력 전압은 입력 전압에 반전된 역상 전압 - vi와 vo 간에 180˚ 위상차를 갖음 ㅇ R1 및 Rf에 흐르는 전류는 같음 - 즉, Ii = If ㅇ 가상 단락 및 가상 접지 상태임 - 즉, v- = v+ = 0 ㅇ 전압 이득 Av는 전적으로 외부 수동소자(Rf/R1)에 의해 결정됨 - 즉, Av = vo/vi = - Rf/R1 ㅇ 반전 증폭기의 입력 저항 : R1 - Rin = vi/i = vi/(vi/R1) = R1 ㅇ 반전 증폭기의 출력 저항 ≒ 0 - Rout ≒ 이상적인 연산증폭기의 출력 저항 = 0 3. [Op Amp] 반전 증폭기의 가상 접지(Virtual Ground)

ㅇ 반전 단자(-)로의 전류 유입은 없고, ㅇ 비반전 단자(+)에서의 접지는, - 두 입력 단자 간에 전압강하를 유발하지 않으므로, ㅇ 따라서, 반전 단자(-)의 전압은 0 이 됨 (즉, 가상 접지) ※ 결국, 전압은 단락 상태, 전류는 개방 상태가 됨 4. [Op Amp] 반전 증폭기의 전압 이득 ㅇ 폐쇄루프이득 Av은 연산증폭기 자체 이득과는 무관 - 전적으로, 연산증폭기 외부에 있는 수동소자 Rf,R1에 의존 . Av = vo/vi = - Rf/R1

5. [Op Amp] 반전 증폭기의 등가 회로

"본 웹사이트 내 모든 저작물은 원출처를 밝히는 한 자유롭게 사용(상업화포함) 가능합니다"

[정보통신기술용어해설]